## **EUROCARD**

**AES/EBU Digital to 2 Mb/s G.703 Network Interface Adapters**

Types DAC-3440 & DAC-3450

Designed and manufactured in Australia

IRT can be found on the Internet at: http://www.irtelectronics.com

## DAC-3440 & DAC-3450

## AES/EBU Digital to 2 Mb/s G.703 Network Interface Adapters.

## **Instruction Manual**

#### **Table of Contents**

| Item                                  | Page |

|---------------------------------------|------|

| Operational Safety                    | 2    |

| General Description                   | 3    |

| Circuit Description                   | 4    |

| Configuration                         | 5    |

| Specifications                        | 6    |

| Installation                          | 7    |

| Front & rear panel connector diagrams | 8    |

| Maintenance & storage                 | 9    |

| Warranty & service                    | 9    |

| Equipment return                      | 9    |

| Drawing list index                    | 10   |

## **Operational Safety:**

## **WARNING**

Operation of electronic equipment involves the use of voltages and currents that may be dangerous to human life. Note that under certain conditions dangerous potentials may exist in some circuits when power controls are in the **OFF** position. Maintenance personnel should observe all safety regulations.

Do not make any adjustments inside equipment with power  $\mathbf{ON}$  unless proper precautions are observed. All internal adjustments should only be made by suitably qualified personnel. All operational adjustments are available externally without the need for removing covers or use of extender cards.

## **General Description.**

The DAC-3440, together with the DAC 3450, forms a transmitter/receiver system which is designed to allow a 20 bit AES/EBU digital audio signal to be distributed via the phone network.

The DAC-3440 converts an AES/EBU digital audio signal into a non-framed G.703 compatible signal.

The DAC-3440 combines the 20 bit audio data with either C data or U data into an output stream at 2.048 Mb/s. This stream is then output as a standard G.703 HDB3 encoded  $75\Omega$  unframed signal.

The DAC-3450 converts a G.703 signal, whose content is formatted as per the output of the DAC-3440, to an AES/EBU data stream. The receiver obtains synchronism with the incoming stream and then separates the audio data from the combined C (or U) data.

The DAC-3450 allows a local reference AES/EBU signal to be input for rate synchronization of the output. With no reference signal present, output rate is automatically set to 48 KHz.

The system can handle mono or stereo 20 bit AES/EBU audio at any rate from 25 KHz to 55 KHz, although it is designed for a nominal 48 KHz.

The system also allows either the Channel (C) or User (U) data to be conveyed.

Front panel LEDs indicate when an AES/EBU signal is present and when the input AES/EBU signal sample rate is 48 KHz on the DAC-3440, and when a valid 2.048 Mb/s G.703 input signal is present and when a valid AES/EBU reference signal is applied to the DAC-3450.

A relay output is provided on each of the rear assemblies for remote status indication for when a valid AES/EBU signal is present or invalid.

A choice of  $75\Omega$  unbalanced or  $110\Omega$  balanced AES/EBU line connections is provided on the rear connector assemblies, settable by an internal link on the main board.

The DAC-3440 and DAC-3450 are fabricated in IRT's standard Eurocard format and may be housed in a variety of IRT Eurocard frames alongside other standard modules.

## Circuit Description.

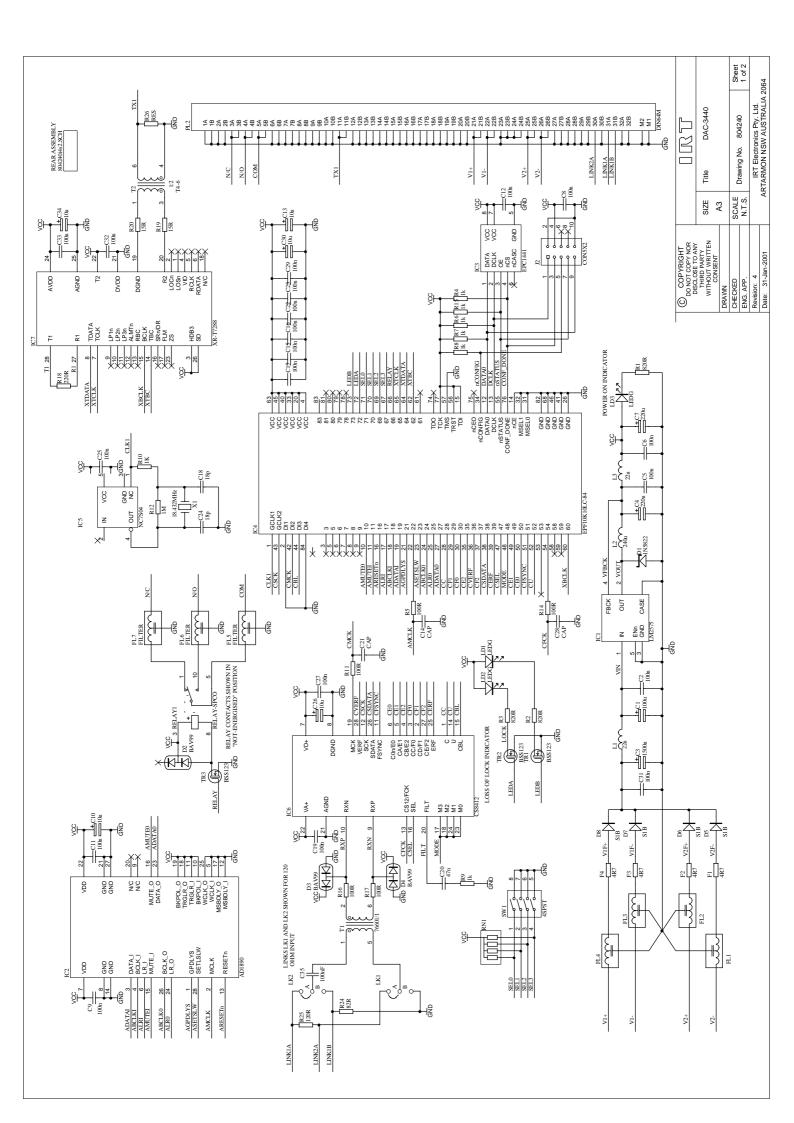

#### **DAC-3440:**

AES/EBU input signal is applied to either the  $75\Omega$  unbalanced or  $110\Omega$  balanced input connector on the rear connector assembly. Links LK1A and LK2A set the input impedance for  $110\Omega$  balanced operation. Links LK1B and LK2B set the input impedance for  $75\Omega$  operation.

The AES/EBU signal is coupled via transformer T1 to IC6, which is an AES/EBU receiver chip. IC2 is a 20 bit AES/EBU resampler chip where the AES signal is resampled at a 48 kHz rate. IC4 is a programmable gate array where processing of the signal takes place to convert the signal into a G.703 format. IC7 is a 2 Mb/s G.703 transmitter chip who's input is fed from IC4. Output is then coupled via transformer T2 to the output connector on the rear connector assembly.

Front panel LEDs, LD1 and LD2, are controlled by IC4 in conjunction with transistors TR1 and TR2. These light up when a valid AES/EBU signal is present and when the sample rate is 48 kHz, respectively.

A relay, RELAY 1, connects to the rear connector assembly to provide the user with alarm/status indications. It is controlled by IC4 in conjunction with transistor TR3. When the N/O contact is connected to common (COM), the system is locked and the AES/EBU input signal is valid. When the N/C contact is connected to common (COM), the power is either off or the AES/EBU input is absent or invalid.

SW1 is a 4 pole DIP switch used for selecting various options. See configuration section for DIP switch settings.

The power supply comprises two half bridge rectifiers formed by diodes D5, D6, D7 and D8 whose rectified outputs are paralleled to provide redundancy. The input to these rectifiers are two independent feeds of 28 Vac (centre tap grounded). These feed a switch-mode regulator, IC1, to give +5 Vdc supply for the circuit.

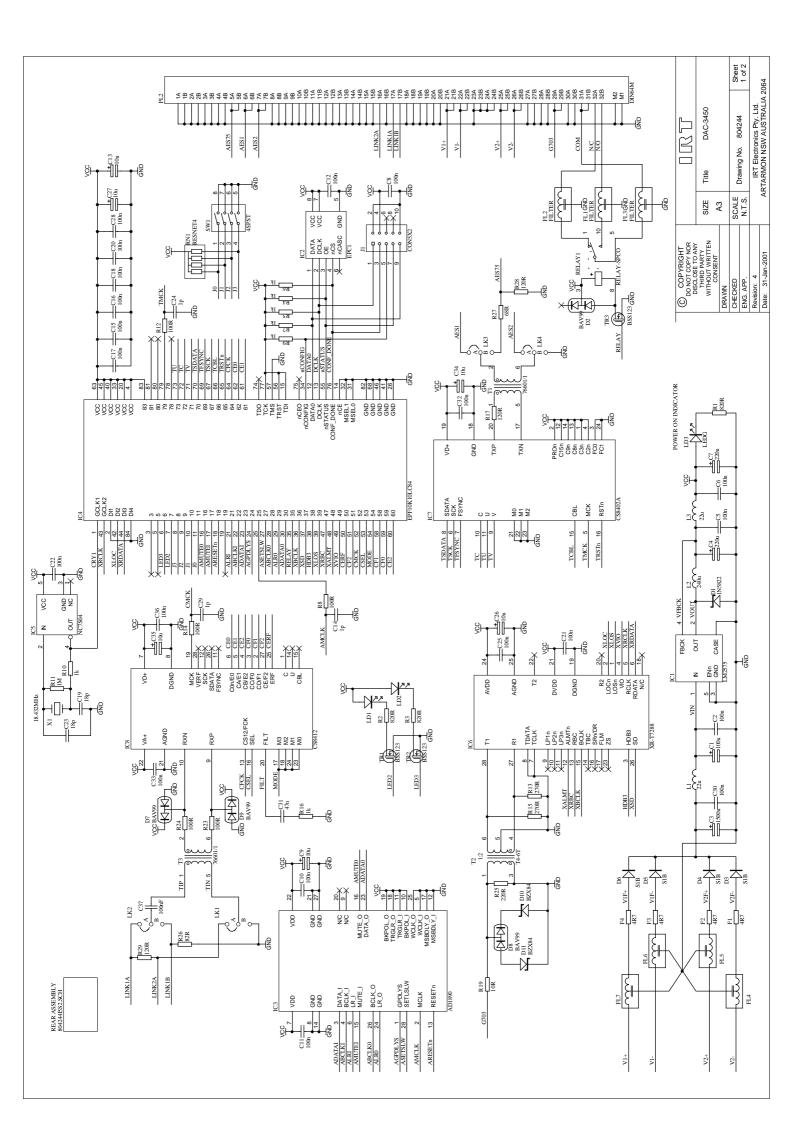

#### **DAC-3450:**

2 Mb/s G.703 signal, as configured by DAC-3440, is fed via transformer T2 to IC6, which is a 2 Mb/s G.703 receiver chip. This then feeds IC4, which is a programmable gate array, where processing of the signal occurs to convert the signal back to the original AES/EBU signal. IC3 acts as a 20 bit AES/EBU resampler.

An optional AES/EBU reference signal can be applied to either the  $75\Omega$  unbalanced or  $110\Omega$  balanced reference input connector on the rear connector assembly. Links LK1A and LK2A set the reference input impedance for  $110\Omega$  balanced operation. Links LK1B and LK2B set the reference input impedance for  $75\Omega$  operation. This is then coupled via transformer T3 to IC8, which is an AES/EBU clock extractor. This referenced clock is then used to reference the output AES/EBU signal. If no reference signal is present, then the onboard crystal oscillator, together with IC5, provides the referencing for the output AES/EBU signal.

IC7 acts as an AES/EBU transmitter. Output is fed via transformer T1 and links LK3 and LK4 to either the  $75\Omega$  unbalanced or  $110\Omega$  balanced output connector. Links LK3A and LK4A set the output impedance for  $110\Omega$  balanced operation. Links LK3B and LK4B set the output impedance for  $75\Omega$  operation.

Front panel LEDs, LD1 and LD2, are controlled by IC4 in conjunction with transistors TR1 and TR2. These light up when a valid 2 Mb/s G.703 and a valid AES/EBU reference signal is present, respectively.

A relay, RELAY 1, connects to the rear connector assembly to provide the user with alarm/status indications. It is controlled by IC4 in conjunction with transistor TR3. When the N/O contact is connected to common (COM), the system is locked and the AES/EBU output signal is valid. When the N/C contact is connected to common (COM), the power is either off or the G.703 input is absent or invalid.

SW1 is a 4 pole DIP switch used for selecting various options. See configuration section for DIP switch settings.

The power supply comprises two half-bridge rectifiers formed by diodes D3, D4, D5 and D6 whose rectified outputs are paralleled to provide redundancy. The input to these rectifiers are two independent feeds of 28 Vac (centre tap grounded). These feed a switch-mode regulator, IC1, to give +5 Vdc supply for the circuit.

# Configuration

## **DAC-3440:**

| Links: | LK1A & LK2A<br>LK1B & LK2B |     | 110 $\Omega$ input operation                              |  |

|--------|----------------------------|-----|-----------------------------------------------------------|--|

|        |                            |     | 75Ω input operation                                       |  |

| SW1    | SW1-1                      | ON  | Long group delay (more tolerant of sample rate changes)   |  |

|        |                            | OFF | Short group delay (more sensitive to sample rate changes) |  |

|        | SW1-2                      | ON  | Fast settling (more sensitive to jitter)                  |  |

|        |                            | OFF | Slow settling (less sensitive to jitter)                  |  |

|        | SW1-3                      | ON  | C data CRC disable                                        |  |

|        |                            | OFF | C data CRC enable                                         |  |

|        | SW1-4                      | ON  | C data transmitted                                        |  |

|        |                            | OFF | U data transmitted                                        |  |

## **DAC-3450:**

| Links: | LK1A & LK2A<br>LK1B & LK2B<br>LK3A & LK4A<br>LK3B & LK4B |                     | 110Ω reference input operation 75Ω reference input operation 110Ω output operation 75Ω output operation                                |

|--------|----------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| SW1    | SW1-1<br>SW1-2<br>SW1-3<br>SW1-4                         | ON<br>OFF<br>-<br>- | Long group delay (more tolerant of sample rate changes) Short group delay (more sensitive to sample rate changes) Unused Unused Unused |

## DAC-3440 & DAC-3450 Specifications

**DAC-3440:**

**Input:** AES/EBU (75 $\Omega$  unbalanced or 110 $\Omega$  balanced)

Input Level 200 mVp-p minimum.

Format AES3-1992 standard.

Sample Rate 25kHz to 55kHz

Input Cable Length >500m 75 $\Omega$  (Belden 8281)

>200m  $110\Omega$  (AES digital high quality shielded pair)

**Output:** 2.048 Mb/s G.703

**DAC-3450:**

**Input:** 2.048 Mb/s G.703

**Reference Input:** AES/EBU (75 $\Omega$  unbalanced or 110 $\Omega$  balanced)

Input Level 200 mVp-p minimum.

Format AES3-1992 standard.

Sample Rate 25kHz to 55kHz

Input Cable Length >500m 75 $\Omega$  (Belden 8281)

>200m  $110\Omega$  (AES digital high quality shielded pair)

**Output:** AES/EBU ( $75\Omega$  unbalanced or  $110\Omega$  balanced)

Format AES3-1992 standard.

**System Performance (End to End):**

Dynamic Range 120 dB (20Hz to 20kHz, -60dB input) THD + N < -88 dB (20Hz to 20kHz, full scale input)

(Fin<sup>1</sup> & Fout<sup>2</sup> between 25 and 55kHz)

< -100 dB (1kHz, full scale input)

(Fin<sup>1</sup> & Fout<sup>2</sup> between 34 and 55kHz)

< -94 dB (10kHz, full scale input)

(Fin<sup>1</sup> & Fout<sup>2</sup> between 34 and 55kHz)

Output signal rise and fall times <20 nS

Frequency Response  $\pm 0.05$  dB 20Hz to 20kHz. (Notes: 1. Fin = sample rate of AES/EBU input to DAC-3440;

2. Fout = sample rate of AES/EBU output from DAC-3450)

Other:

Power requirement per unit 28 Vac CT (14-0-14) or  $\pm$  16 Vdc. (3.5VA)

Temperature range 0 - 50° C ambient.

Connectors Unbalanced BNC.

Balanced Removable screw terminal blocks.

Mechanical Suitable for mounting in IRT 19" rack chassis with input output and

power connections on the rear panel.

Finish: Front panel Grey enamel, silk-screened black lettering & red IRT logo.

Rear assembly Detachable silk-screened PCB with direct mount connectors to Eurocard

and external signals.

Dimensions 30 mm x 3 U x 220 mm IRT Eurocard. Accessories supplied with module Rear connector

Due to our policy of continuing development these specifications are subject to change without notice.

#### Installation

#### **Pre-installation:**

#### **Handling:**

This equipment may contain or be connected to static sensitive devices and proper static free handling precautions should be observed.

Where individual circuit cards are stored, they should be placed in antistatic bags. Proper antistatic procedures should be followed when inserting or removing cards from these bags.

#### **Power:**

AC mains supply: Ensure that operating voltage of unit and local supply voltage match and that correct rating

fuse is installed for local supply.

DC supply: Ensure that the correct polarity is observed and that DC supply voltage is maintained within

the operating range specified.

#### **Earthing:**

The earth path is dependent on the type of frame selected. In every case particular care should be taken to ensure that the frame is connected to earth for safety reasons. See frame manual for details.

**Signal earth:** For safety reasons a connection is made between signal earth and chassis earth. No attempt should be made to break this connection.

#### **Installation in frame or chassis:**

See details in separate manual for selected frame type.

#### **Signal Connections**

Signal connections are made to the connectors on the rear panels of the DAC-3440 and DAC-3450.

The input signal for the DAC-3440 can be either 75 ohms unbalanced terminating or 110 ohms balanced terminating. The input signal for the DAC-3450 is 75 ohms unbalanced terminating while the reference input signal for the DAC-3450 can be either 75 ohms unbalanced terminating or 110 ohms balanced terminating. The **input selection** for the DAC-3440 is done by links **LK1**, **LK2** on the module pcb near pin 32 of the input connector and the **reference input selection** for the DAC-3450 is done by links **LK1**, **LK2** on the module pcb near pin 17 of the input connector. Move the links provided to the 75 or 110 positions marked on the board as required. The input signal is then connected to the appropriate input connector on the rear panel.

The output signal for the DAC-3440 is 75 ohms unbalanced terminating. The output signal for the DAC-3450 can be either 75 ohms unbalanced terminating or 110 ohms balanced terminating, the **output selection** is done by links **LK3**, **LK4** on the module pcb near pin 6 of the output connector. Move the links provided to the 75 or 110 positions marked on the board as required. The output signal is then connected to the appropriate output connector on the rear panel.

NOTE: If it is necessary to remove a component from the circuit board during maintenance IT IS ESSENTIAL TO ADD SOME SOLDER TO THE COMPONENT SOLDER JOINTS BEFORE REMOVAL IS ATTEMPTED. This will add some solder flux to the joint and allow the heat from the iron to flow quickly into the joint and prevent localised overheating and damage to the circuit board. Rear assemblies may be removed for maintenance. Make sure that extraction force is applied equally and steadily at the top and bottom of the rear assembly. SHOULD THIS NOT BE DONE THERE IS A GOOD CHANCE THAT YOU WILL BEND THE MODULE CONNECTOR PINS making it very difficult to re-install the rear assembly.

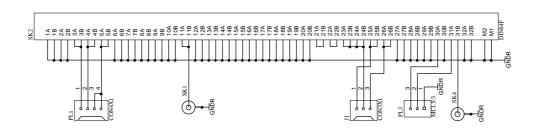

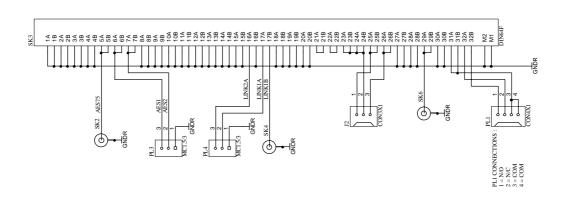

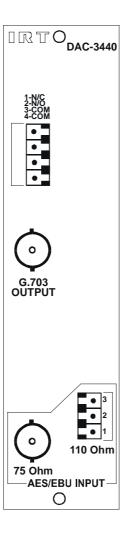

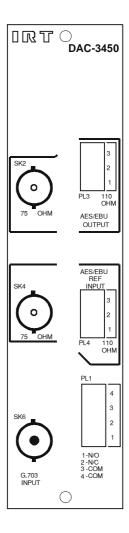

## Front & rear panel connector diagrams

The following front panel and rear assembly drawings are not to scale and are intended to show relative positions of connectors, indicators and controls only.

## **Maintenance & storage**

#### **Maintenance:**

No regular maintenance is required.

Care however should be taken to ensure that all connectors are kept clean and free from contamination of any kind. This is especially important in fibre optic equipment where cleanliness of optical connections is critical to performance.

#### **Storage:**

If the equipment is not to be used for an extended period, it is recommended the whole unit be placed in a sealed plastic bag to prevent dust contamination. In areas of high humidity a suitably sized bag of silica gel should be included to deter corrosion.

Where individual circuit cards are stored, they should be placed in antistatic bags. Proper antistatic procedures should be followed when inserting or removing cards from these bags.

## Warranty & Service

Equipment is covered by a limited warranty period of three years from date of first delivery unless contrary conditions apply under a particular contract of supply. For situations when "**No Fault Found**" for repairs, a minimum charge of 1 hour's labour, at IRT's current labour charge rate, will apply, whether the equipment is within the warranty period or not.

Equipment warranty is limited to faults attributable to defects in original design or manufacture. Warranty on components shall be extended by IRT only to the extent obtainable from the component supplier.

#### **Equipment return:**

Before arranging service, ensure that the fault is in the unit to be serviced and not in associated equipment. If possible, confirm this by substitution.

Before returning equipment contact should be made with IRT or your local agent to determine whether the equipment can be serviced in the field or should be returned for repair.

The equipment should be properly packed for return observing antistatic procedures.

The following information should accompany the unit to be returned:

- 1. A fault report should be included indicating the nature of the fault

- 2. The operating conditions under which the fault initially occurred.

- 3. Any additional information, which may be of assistance in fault location and remedy.

- 4. A contact name and telephone and fax numbers.

- 5. Details of payment method for items not covered by warranty.

- 6. Full return address.

- 7. For situations when "**No Fault Found**" for repairs, a minimum charge of 1 hour's labour will apply, whether the equipment is within the warranty period or not. Contact IRT for current hourly rate.

Please note that all freight charges are the responsibility of the customer.

The equipment should be returned to the agent who originally supplied the equipment or, where this is not possible, to IRT direct as follows.

Equipment Service IRT Electronics Pty Ltd 26 Hotham Parade ARTARMON N.S.W. 2064 AUSTRALIA

Phone: 61 2 9439 3744 Fax: 61 2 9439 7439

Email: service@irtelectronics.com

# **Drawing List Index**

| Drawing # | Sheet# | Description                                                       |

|-----------|--------|-------------------------------------------------------------------|

| 804240    | 1      | DAC-3440 AES/EBU to G.703 Converter circuit diagram               |

|           | 2      | E                                                                 |

| 804240    | 2      | DAC-3440 AES/EBU to G.703 Converter rear assembly circuit diagram |

| 804244    | 1      | DAC-3450 G.703 to AES/EBU Converter circuit diagram               |

| 804244    | 2      | DAC-3450 G.703 to AES/EBU Converter rear assembly circuit diagram |