# **IRT Eurocard**

Types MFC-3485 & MFC-3465

ASI / G.703 Network Interface Adaptors

Designed and manufactured in Australia

IRT can be found on the Internet at: http://www.irtelectronics.com

# IRT Eurocard Types MFC-3485 and MFC-3465 ASI / G.703 Network Interface Adaptors

### **Instruction Book**

### **Table of Contents**

| Section                               | Page |

|---------------------------------------|------|

| Declaration of Conformity             | 2    |

| General description                   | 3    |

| Block diagram                         | 4    |

| Technical specifications              | 5    |

| Technical description                 | 6    |

| MFC-3485                              | 6    |

| MFC-3465                              | 7    |

| Configuration                         | 8    |

| Links                                 | 8    |

| MFC-3485                              | 8    |

| MFC-3465                              | 8    |

| Installation                          | 9    |

| Operational safety                    | 9    |

| Pre-installation                      | 9    |

| Installation in frame or chassis:     | 9    |

| Connections:                          | 9    |

| MFC-3485:                             | 9    |

| MFC-3465:                             | 10   |

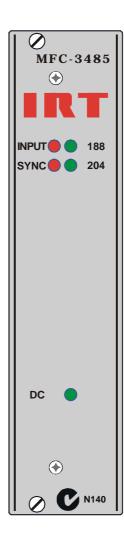

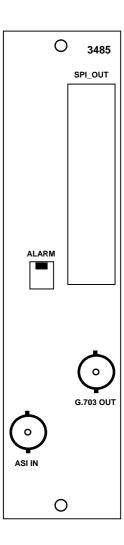

| Front & rear panel connector diagrams | 11   |

| Operation                             | 12   |

| Front indicators                      | 12   |

| Maintenance & storage                 | 13   |

| Warranty & service                    | 13   |

| Equipment return                      | 13   |

| Characteristics of signal types       | 14   |

| Coding characteristics                | 14   |

| G.703                                 | 14   |

| Synchronous Parallel Interface        | 14   |

| Asynchronous Serial Interface         | 15   |

| MPEG-2 transport layer coding         | 16   |

| Electrical characteristics            | 18   |

| G.703                                 | 18   |

| SPI                                   | 19   |

| ASI                                   | 19   |

| References                            | 20   |

| Glossary of terms                     | 21   |

| Drawing index                         | 22   |

This instruction book applies to units later than S/N 9900000.

### **Declaration of Conformity**

Both the MFC-3465 and MFC-3485 meet both C-Tick and CE standards and satisfies the essential requirements of directives 73/23/EEC and 89/336/EEC as modified by directives 93/68/EEC, 92/31/EEC and 93/97/EEC.

### **General description**

The MFC-3485 and MFC-3465 are part of a family of data transcoders for converting between the commonly used MPEG2 Transport Stream formats in the broadcast industry for video distribution.

Any ASI (Asynchronous Serial Interface) input with a payload data rate within the range of 1.5 to 39 Mb/s will be converted to a B3ZS encoded 44.736 Mb/s unformatted data stream by the MFC-3485/45. The output shape may be either "High" or "Low".

The MFC-3465/45 provides the complementary conversion from a data payload within a 45 Mb/s B3ZS G.703 stream to ASI format.

For HDB3 34.368 Mb/s rates the MFC-3485/34 and MFC-3465/34 may be used. These accommodate data payloads in the range of 1.5 to 30 Mb/s.

The transmitted streams are padded up to the required transmission rate with bytes of a unique pattern, which are removed at the receiver so that the original ASI payload rate is restored.

In the absence of a valid MPEG ASI input the MFC-3485 will transmit "all ones".

IRT's 34XX series of adapters provide a modular approach to connecting between the different transport types.

The 34XX series find particular application in CATV Headends where equipment from different manufacturers uses different formats. They may also be used for monitoring connections to test equipment.

In addition, the DDC-3470 provides facilities for changing certain coding features of the MPEG transport stream to ensure compatibility between signals.

| Product Selection Chart |                |                    |            |            |  |  |

|-------------------------|----------------|--------------------|------------|------------|--|--|

| Product                 | Data rates     | Input              | Outputs    |            |  |  |

| DDC-3460                | /34            | G.703-E3           | ASI        |            |  |  |

|                         | /45            | G.703-DS-3         | ASI        |            |  |  |

| DDC-3471                |                | SPI                | SPI        | ASI        |  |  |

|                         |                |                    |            |            |  |  |

| DDC-3480                | /34            | ASI                | G.703-E3   |            |  |  |

|                         | /45            | ASI                | G.703-DS-3 |            |  |  |

| DDC-3330                | 1.5 to 50 Mb/s | ASI                | SPI        |            |  |  |

| DDC-3340                | 1.5 to 50 Mb/s | SPI                | ASI        |            |  |  |

| MFC-3465                | /34            | G.703-E3           | ASI        |            |  |  |

|                         | /45            | G.703-DS-3         | ASI        |            |  |  |

| MFC-3485                | /34            | ASI 1.5 to 30 Mb/s |            | G.703-E3   |  |  |

|                         | /45            | ASI 1.5 to 39 Mb/s |            | G.703-DS-3 |  |  |

Note: The DDC-3471 allows Reed Solomon correction and the insertion or removal of interleaving and MPEG2 transport stream spectrum shaping randomisation. This makes it an ideal adjunct to test equipment or for matching signal from various sources using different encoding options.

### **Features:**

- Input rate stuffing to G.703 rates.

- Modular format compatible with IRT fibre optic, distribution amplifier and switcher modules.

- Suitable for Single Frequency Network (SFN) use

### **Applications:**

- Conversion of variable rates of DVB ASI to G.703, and for transport via Telecom circuits.

- Block length indication and error detection.

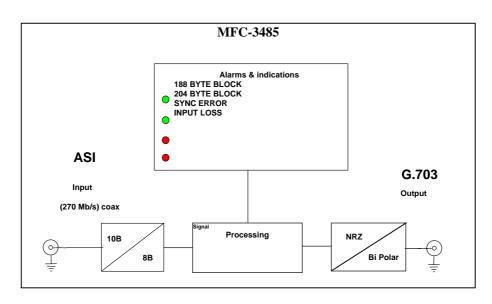

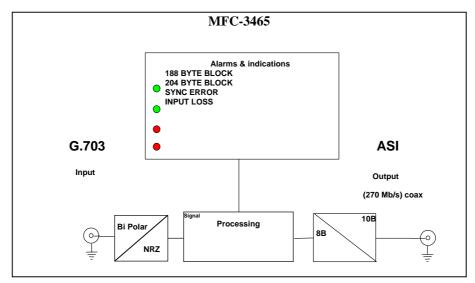

# **Block diagrams**

## **Technical Specifications**

(Preliminary)

MFC-3485/45:

$\begin{array}{ccc} \textbf{Input:} & 1 \text{ x ASI-C} \\ & \textbf{Impedance} & 75\Omega \\ & \textbf{Level} & 800 \text{ mVp-p.} \\ & \textbf{Data rate} & <39 \text{ Mb/s} \\ \end{array}$

**Output:** 1 x G.703

Electrical characteristics B3ZS encoding

Data Rate 44.736 Mb/s

Output Level High or Low

MFC-3465/45:

Input: 1 x G.703.

Electrical characteristics B3ZS encoded.

Data rate 44.736 Mb/s

Output: 1 x ASI-C

Impedance75ΩLevel800 mVp-p.Added PCR JitterLess than 200nS.

MFC-3485/34:

Input: 1 x ASI-C

$\begin{array}{ccc} & Impedance & 75\Omega \\ & Level & 800 \text{ mVp-p.} \\ & Data \text{ rate} & <30 \text{ Mb/s} \\ \hline \textbf{Output:} & 1 \text{ x G.703,} \\ & Electrical characteristics} & HDB3 \text{ encod} \\ \end{array}$

Electrical characteristics HDB3 encoding Data Rate 34.368 Mb/s

MFC-3465/34:

**Input:** 1 x G.703.

$\begin{array}{ccc} & \text{Electrical characteristics} & \text{HDB3 encoded.} \\ & \text{Data rate} & 34.368 \text{ Mb/s} \\ \\ \textbf{Output:} & 1 \text{ x ASI-C} \\ & \text{Impedance} & 75\Omega \end{array}$

Level 800 mVp-p.

Added PCR Jitter Less than 240nS.

Connectors BNC

Power Requirements 28 Vac CT (14-0-14) or  $\pm$  16 Vdc.

Power consumption <5 VA.

Other:

Temperature range  $0 - 50^{\circ}$  C ambient.

Mechanical Suitable for mounting in IRT 19" rack chassis with input, output and power connections

on the rear panel.

Finish: Front panel Grey enamel, silk-screened black lettering & red IRT logo.

Rear assembly Detachable silk-screened PCB with direct mount connectors to Eurocard and external

signals.

Dimensions 6 HP x 3 U x 220 mm IRT Eurocard.

Supplied accessories Rear connector assembly.

Related products DDC-3460 - G.703 to SPI, ASI.

DDC-3480 - ASI to G.703

DVT/R-3210 ASI fibre optic link. TME-6 module extender card.

Optional accessories TME-6 module extender card.

Due to our policy of continuing development, these specifications are subject to change without notice.

### **Technical description**

The MFC-3485 and MFC-3465 form a system for encoding and decoding the data in an ASI data stream for transport in a G.703 stream. The MFC-3485 takes ASI data rates from 1.5 to 30 Mb/s and adds stuffing bytes to convert the signal to run on a 34 Mb/s (E-3) G.703 system (MFC-3485/34, 34 Mb/s version) or ASI data rates from 1.5 to 39 Mb/s and adds stuffing bytes to convert the signal to run on a 45 Mb/s (DS-3) G.703 system (MFC-3485/45, 45 Mb/s version). The MFC-3465 decodes and removes the stuffing bytes to restore the original ASI data steam.

As the MFC-3485 does the original encoding, it will be described in detail first.

### **MFC-3485**

#### **ASI Input**

The input ASI signal passes through an automatic line equalisation circuit, U1. The purpose of this equaliser is to restore both the signal level and the leading and trailing edges of the digital signal so that signal jitter is reduced prior to feeding the next stage, U2, which is a serial to parallel data converter which feeds the main logic processor, U5.

### Logic processing, reclocking and error detection.

The main logic processing, reclocking, error detection and operational interfacing are all performed by logic circuits within a custom programmed large scale logic array. The internal logic and functions of this IC are too complex to describe in detail and the following is intended as a guide to function only. Data rates are byte stuffed here to bring the rate up to standard G.703 rates depending on the version of card, i.e. 34 Mb or 45 Mb.

#### Data loss detection.

Receipt of an invalid ASI byte is considered a loss of data.

### **Sync Error**

ASI packet sync has been lost at the output of the FIFO.

#### 188 TS Sync length indicator

If the number of bytes between TS packet syncs is 188 then the 188 LED lights. When either a loss of input or sync loss is detected, this LED is extinguished.

### 204 TS Sync length indicator

If the number of bytes between TS packet syncs is 204 then the 204 LED lights. When either a loss of input or sync loss is detected, this LED is extinguished.

### Alarm relay

An alarm output is available on the rear assembly using a two pin connector.

The relay contact will short circuit the two pins on the rear assembly when the selected alarm condition occurs, selectable by link LK3 (see configuration section) or there is a loss of power to the module.

#### G.703 Output

U4 is a G.703 data driver IC feeding a transformer to give an output on the rear connector unit. Link settings set the output for either HDB3 for the 34 Mb version or B3ZS for the 45 Mb (link LK1) and whether the output is shaped or unshaped (link LK2). See configuration section for settings.

### **SPI Output**

True SPI output is also provided on rear connector unit.

#### **MFC-3465**

Converts unframed stuffed G.703 into ASI-C. This module complements the MFC-3485 ASI-C to G.703 converter and stuffer, removing the encoded stuffed bytes from the G.703 stream to give the original encoded ASI stream. This module does not perform any processing (e.g. RS coding, interleaving, energy dispersion correction etc) but rather decodes the G.703 input and detects MPEG TS sync errors.

### **G.703 Input**

The input G.703 signal, originally encoded by the MFC-3485, is applied to the rear panel connector and passes to the input transformer and integrated line receiver, U3. This receiver chip provides automatic line equalisation and derives  $\pm$  1 and clock signals of the input G.703 signal for processing in the following stages. In order for line equalisation to take place, link LK2 must be installed.

### Logic processing, reclocking and error detection.

The main logic processing, reclocking, error detection and operational interfacing are all performed by logic circuits within a custom programmed large scale logic array. The internal logic and functions of this IC are too complex to describe in detail and the following is intended as a guide to function only.

#### Data loss detection.

If the input level is insufficient for correct operation or if more than 180 1's occur in a row then data loss is deemed to have occurred.

#### **Sync Error**

After 2 consecutive TS syncs are missed a TS Sync Error is deemed to have occurred. The Sync error is reset only after 5 consecutive TS syncs have been detected. The SYNC Error LED lights when a Sync error has been detected and remains lit for approximately 300 ms after the Sync error has been reset.

#### 188 TS Sync length indicator

If the number of bytes between TS syncs is 188 then the 188 LED lights. When either a loss of input or sync loss is detected, this LED is extinguished.

### 204 TS Sync length indicator

If the number of bytes between TS syncs is 204 then the 204 LED lights. When either a loss of input or sync loss is detected, this LED is extinguished.

### Alarm relay

An alarm output is available on the rear assembly using a two pin connector.

The relay contact will short circuit the two pins on the rear assembly when the selected alarm condition occurs, selectable by link LK3 (see configuration section) or there is a loss of power to the module.

### **ASI Output**

Processed data, minus the added stuffing bits originally added to the signal steam by the MFC-3485, is parallel loaded to a parallel to serial converter, U2, before feeding a driver, U1, to give the original payload rate ASI signal on the rear connector.

### Configuration

### Links:

### MFC-3485

**LK 1:** IN HDB3 output. Set IN for MFC-3485/34 (34 Mb/s) version only – factory set.

OUT B3ZS output. Set OUT for MFC-3485/45 (45 Mb/s) version only – factory set.

LK 2: IN DS3 shaped output for <225 feet, MFC-3485/45 (45 Mb/s) version.

OUT DS3 unshaped output for >225 feet, MFC-3485/45 (45 Mb/s) version.

Note: Leave out on MFC-3485/34 (34 Mb/s) version.

**LK 3:** LEFT Relay Alarm set to indicate on Loss of Signal. (if fitted) RIGHT Relay Alarm set to indicate on Sync Error.

### MFC-3465

**LK 2:** IN Enable cable input equalisation.

OUT Disable cable input equalisation.

**LK 3:** LEFT Relay Alarm set to indicate on Loss of Signal. (if fitted) RIGHT Relay Alarm set to indicate on Sync Error.

### **Installation**

### **Operational Safety:**

### WARNING

Operation of electronic equipment involves the use of voltages and currents that may be dangerous to human life. Note that under certain conditions dangerous potentials may exist in some circuits when power controls are in the **OFF** position. Maintenance personnel should observe all safety regulations.

Do not make any adjustments inside equipment with power **ON** unless proper precautions are observed. All internal adjustments should only be made by suitably qualified personnel. All operational adjustments are available externally without the need for removing covers or use of extender cards.

### **Pre-Installation:**

### **Handling:**

This equipment may contain or be connected to static sensitive devices and proper static free handling precautions should be observed.

Where individual circuit cards are stored, they should be placed in antistatic bags and proper antistatic procedures should be followed when inserting or removing cards from these bags.

### Power:

**AC mains supply:** Ensure that operating voltage of unit and local supply voltage match and that correct rating fuse is installed for local supply.

### **Earthing:**

Particular care should be taken to ensure that the frame is connected to earth for safety reasons.

Signal earth: For safety reasons a connection is made between signal earth and chassis earth. No attempt should be made to break this connection.

### **Installation in frame or chassis:**

See details in separate manual for selected frame type.

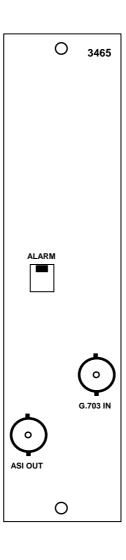

### **Connections:**

### **Signal connections:**

### MFC-3485

#### **ASI** input:

This BNC input is terminated in 75 Ohms. Input cable compensation is automatic for up to 300 metres of high quality 75 Ohm coaxial cable (Belden 8281 equivalent). No adjustments are required.

### **G.703 output:**

This BNC output has a 75 Ohms characteristic output impedance. Cable must be terminated in 75 Ohms at the connected load.

Link setting, LK1, sets unit for either HDB3 or B3ZS output.

**LK1** IN HDB3 output, MFC-3485/34 (34 Mb/s) version.

OUT B3ZS output, MFC-3485/45 (45 Mb/s) version.

Note: LK1 does not change unit from 34 Mb/s operation to 45 Mb/s operation or vice-versa.

For the MFC-3485/45 a choice of shaped or unshaped output is available. This is set by link LK2 and should be set to correspond to the length of cable connected to the output. This is necessary only if a shaped characteristic is

required for short cable lengths. Where the connected equipment has automatic equalisation (such as IRT DA's and converters) this is not required.

**LK2** IN DS3 shaped output for <225 feet, MFC-3485/45 OUT DS3 unshaped output for >225 feet, MFC-3485/45

Note: Leave out on MFC-3465/34 (34 Mb/s) version.

### **Alarm connections:**

Alarm relay output (if fitted).

Closed contacts represent either a Loss of Input signal or Loss of Sync, selectable by link LK3, or Loss of Power.

#### MFC-3465

### **G.703** input:

This BNC input is terminated in 75 Ohms. Input cable compensation is automatic for up to 450 feet of 75 Ohm coaxial cable (Belden 8281 equivalent). Input equalisation can be enabled or disabled by the addition or removal of link LK2.

### **ASI output:**

This BNC output has a 75 Ohms characteristic output impedance. Only high quality 75 Ohm coaxial cable (Belden 8281 or 1694A equivalent) should be used. No adjustments are required, but cable must be terminated in 75 Ohms at the connected load.

### **Alarm connections:**

Alarm relay output (if fitted).

Closed contacts represent either a Loss of Input signal or Loss of Sync, selectable by link LK3, or Loss of Power.

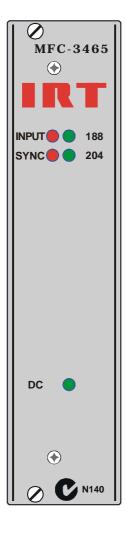

### Front & rear panel connector diagrams

The following front panel and rear assembly drawings are not to scale and are intended to show relative positions of connectors, indicators and controls only.

### **Operation**

There are no operational controls for these modules. Setting up consists only of connecting the input and selected output. Once this is done the front panel indicators should react and the output should present the correct format signal.

Any change in signal will be indicated by the front panel LED's and or alarm output as outlined below.

### **Front indicators:**

### **Input loss alarm:**

This LED lights when there is a loss of input signal or coding errors occur on the input stream.

#### Sync loss alarm:

This LED lights for at least 300 ms when two or more MPEG-2 TS sync bytes are absent. The LED extinguishes when five or more correct SYNC bytes are detected.

### 188 byte indicator:

This LED lights when a valid MPEG-2 TS stream containing 188 bytes between sync bytes is detected.

### 204 byte indicator:

This LED lights when a valid MPEG-2 TS stream containing 204 bytes between sync bytes is detected.

### **Maintenance & storage**

### **Maintenance:**

No regular maintenance is required.

Care however should be taken to ensure that all connectors are kept clean and free from contamination of any kind. This is especially important in fibre optic equipment where cleanliness of optical connections is critical to performance.

### **Storage:**

If the equipment is not to be used for an extended period, it is recommended the whole unit be placed in a sealed plastic bag to prevent dust contamination. In areas of high humidity a suitably sized bag of silica gel should be included to deter corrosion.

Where individual circuit cards are stored, they should be placed in antistatic bags. Proper antistatic procedures should be followed when inserting or removing cards from these bags.

### Warranty & Service

Equipment is covered by a limited warranty period of three years from date of first delivery unless contrary conditions apply under a particular contract of supply. For situations when "**No Fault Found**" for repairs, a minimum charge of 1 hour's labour, at IRT's current labour charge rate, will apply, whether the equipment is within the warranty period or not.

Equipment warranty is limited to faults attributable to defects in original design or manufacture. Warranty on components shall be extended by IRT only to the extent obtainable from the component supplier.

### **Equipment return:**

Before arranging service, ensure that the fault is in the unit to be serviced and not in associated equipment. If possible, confirm this by substitution.

Before returning equipment contact should be made with IRT or your local agent to determine whether the equipment can be serviced in the field or should be returned for repair.

The equipment should be properly packed for return observing antistatic procedures.

The following information should accompany the unit to be returned:

- 1. A fault report should be included indicating the nature of the fault

- 2. The operating conditions under which the fault initially occurred.

- 3. Any additional information, which may be of assistance in fault location and remedy.

- 4. A contact name and telephone and fax numbers.

- 5. Details of payment method for items not covered by warranty.

- 6. Full return address.

- 7. For situations when "**No Fault Found**" for repairs, a minimum charge of 1 hour's labour will apply, whether the equipment is within the warranty period or not. Contact IRT for current hourly rate.

Please note that all freight charges are the responsibility of the customer.

The equipment should be returned to the agent who originally supplied the equipment or, where this is not possible, to IRT direct as follows.

Equipment Service IRT Electronics Pty Ltd 26 Hotham Parade ARTARMON N.S.W. 2064 AUSTRALIA

Phone: 61 2 9439 3744 Fax: 61 2 9439 7439

Email: service@irtelectronics.com

### **Characteristics of signal types**

### **Coding characteristics**

### G.703:

The **HDB3** (High Density Bi-polar of order 3) code as defined in G.703 for 34,368 Kbits/s is as follows:

Binary 1 bits are represented by alternate positive and negative pulses and binary 0 bits by spaces. Exceptions are made when strings of successive 0 bits occur in the binary signal.

Each block of 4 successive zeros is replaced by 000V or B00V where B is an inserted pulse of the correct polarity and V is an inserted pulse violating the polarity rule. The choice of 000V or B00V is made so that the number of B pulses between consecutive V pulses is odd so that successive V pulses are of alternate polarity and so no DC component is introduced.

The **B3ZS** (Bipolar with Three Zero Substitution) (Also designated **HDB2** - High Density Bi-polar of order 2) code as defined in G.703 for 44,736 Kbits/s is as follows:

Binary 1 bits are represented by alternate positive and negative pulses and binary 0 bits by spaces. Exceptions are made when strings of successive 0 bits occur in the binary signal.

Each block of 3 successive zeros is replaced by 00V or B0V. The choice of 00V or B0V is made so that the number of B pulses between consecutive V pulses is odd, so that successive V pulses are of alternate polarity and so no DC component is introduced.

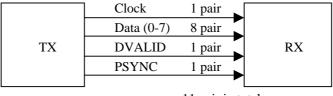

### **Synchronous Parallel Interface (SPI)**

SPI is a system for parallel transmission of variable data rates. The data transfer is synchronised to the Byte clock of the MPEG transport stream.

The data to be transmitted are MPEG-2 transport packets. The data signals are synchronised to the clock depending on the transmission rate.

The parallel interface has three allowable transmission formats:

188 byte packets

204 Byte packets (188 data Bytes + 16 dummy Bytes)

204 byte packets (188 data Bytes + 16 additional valid Bytes)

The clock, data and synchronisation signals are transmitted in parallel. They comprise 8 data bits together with one (MPEG-2) PSYNC signal and a DVALID signal.

The DVALID signal indicates in the 204 Byte mode that the additional space is filled with dummy Bytes.

All signals are synchronous to the clock signal. The signals are coded in NRZ form.

The clock is a square wave signal where the 0-1 transition represents the data transfer time. The clock frequency depends on the transmission rate. The frequency corresponds to the useful bitrate of the MPEG2 transport layer and shall not exceed 13.5 MHz.

= 11 pair in total.

### **Electrical characteristics of the interface**

Each of the eleven line drivers (source) has a balanced output and each line receiver (destination) a balanced input employing LVDS drivers / receivers. All digital signal time intervals are measured between the half-amplitude points.

### Logic convention

A binary 1 is represented by the non-inverted output being positive with respect to the inverted output. A binary 0 is represented by the non-inverted output being negative with respect to the inverted output.

### **Asynchronous Serial Interface (ASI)**

The Asynchronous Serial Interface (ASI) provides a system for serial encoded transmission of different data rates with a constant transmission rate of 270 Mbit/s.

The ASI standard supports coaxial cable and multi-mode fibre-optic cable (using LED emitters).

#### **ASI Protocol Architecture Description**

The ASI protocol is divided into three architectural layers: Layer-0, Layer-1 and Layer-2.

MPEG Transport Packets form the top layer (Layer 2), and the bottom layers are based upon the Fibre Channel Standard (Layers 1 and 0). Layer 2 is defined using the MPEG-2 Standard ISO/IEC 13818-1 (Systems). Layers 1 and 0 are based upon a subset of ANSI Standard X3T11/ Levels FC-1 and FC-0.

### **Layer-O: Physical Requirements**

The physical Layer defines the transmission media, the drivers and receivers, and the transmission speeds. The physical interface provides for both LED-driven multimode fibre and copper coaxial cable.

### **Line Rates and Bit Timing**

The encoded line rate with the 8B/10B block code is 270 Mbit/s which results in a media transmission rate of 270 MBaud. At the transmitter, the serialisation is done using a fixed oscillator to establish this 270 MBaud rate from which a phase-locked Byte clock is derived and used to shift in parallel Bytes.

Receivers recover the serial transmission clock. A phase-locked Byte clock is derived from this recovered serial bit clock and is used to shift parallel Bytes out to Layer- 1 processing elements. It is required that the encoded line rate shall be 270 MBaud  $\pm 100$  ppm.

#### **Layer-1 Data Encoding**

The ASI Transmission Layer 1 deals with encoding/decoding aspects, which are independent of the transmission medium characteristics. The encoding method utilised is specified in the fibre channel document X3T11

At Layer-1, Bytes are 8B/10B coded, which produces one 10-bit word for each 8-bit Byte presented.

The 8B/10B transmission coding provides for both a self checking capability and Byte synchronisation of the link. The 10B transmission code is defined in terms of "disparity": the difference in the number of "1" bits and "0" bits in the transmitted serial data stream. The disparity characteristics of the code maintain DC balance.

Special characters are defined as extra code points beyond the need to encode a Byte of data. One in particular is used to establish Byte synchronisation in the ASI transmission link.

The 10-bit words are then passed through a parallel-to-serial converter, which operates at a fixed output bit-rate of 270 Mbit/s.. If the converter requests a new input word and the data source does not have one ready, a synchronisation word is inserted. These sync words are ignored by receive equipment.

The resulting serial bit stream is passed to the output driver circuit for coaxial or fibre-optic cable.

Receive data arriving on a coaxial cable or fibre is first coupled to a circuit, which recovers clock and data.

Recovered serial data bits are passed to a 10B/8B decoder that converts the 10-bit transmission words back into the 8-bit Bytes originally transmitted. In order to recover Byte alignment, the 10B/8B decoder initially searches for synchronisation words. Once found, the start of the synchronisation word marks the boundary of subsequent received data words and establishes proper Byte-alignment of decoder output Bytes.

NOTE - The ASI coding is sensitive to logical inversion of the transmitted bits. Therefore, to ensure correct operation, care must be taken that equipment interface circuitry of the non-inverting type is used.

The **Bit-Error-Rate (BER) Performance** shall be less than one part in  $10^{13}$ .

### **Layer-2 Transport Protocol**

The ASI Transmission Layer-2 standard uses the MPEG-2 Transport Stream Packet as defined in ISO/IEC 13818-1 (Systems) as its basic message unit. Optionally the RS coded Byte structure as specified in ETS 300 429 is also supported.

Data to be transmitted are presented in Byte-synchronised form as MPEG-2 Transport packets. Transport Packets may be presented to Layer-2 either as a burst of contiguous Bytes, or as individual Bytes spread out in time.

The ASI Interface Layer-2 definition employs the MPEG-2 Transport Stream packet syntax with the additional requirement that every Transport Packet shall be preceded with at least two synchronisation characters. This allows re-sync within one transport packet in the event that a line disturbance causes loss of sync.

### **MPEG-2** transport layer coding

The MPEG-2 Transport Layer is defined in ISO/IEC DIS 13818-1 [1]. The Transport Layer for MPEG-2 data is comprised of packets having 188 Bytes, with one Byte for synchronisation purposes, three Bytes of header containing service identification, scrambling and control information, followed by 184 Bytes of MPEG-2 or auxiliary data.

The framing organisation is based on the MPEG-2 transport packet structure.

### **Channel coding**

To achieve the appropriate level of error protection required for cable transmission of digital data, a FEC based on Reed-Solomon encoding is used. In contrast to the Baseline System for satellite described in ETS 300 421, no convolutional coding is applied to cable transmission. Protection against burst errors is achieved by the use of Byte interleaving.

### Randomisation for spectrum shaping (Scrambling)

The System input stream is organised in fixed length packets (see figure 2), following the MPEG-2 transport multiplexer. The total packet length of the MPEG-2 transport MUX packet is 188 Bytes. This includes 1 sync-word Byte (i.e. 47<sub>HEX</sub>). The processing order at the transmitting side shall always start from the MSB (i.e. 0) of the sync word-Byte (i.e. 01000111).

In order to comply with the System for satellite, (see ETS 300 421) and to ensure adequate binary transitions for clock recovery, the data at the output of the MPEG-2 transport multiplex is randomised.

The polynomial for the Pseudo Random Binary Sequence (PRBS) generator is:

$$1 + X^{14} + X^{15}$$

Loading of the sequence 100101010000000" into the PRBS registers, is initiated at the start of every eight transport packets. To provide an initialisation signal for the de-scrambler, the MPEG-2 sync Byte of the first transport packet in a group of eight packets is bitwise inverted from  $47_{\text{HEX}}$  to  $88_{\text{HEX}}$ .

The first bit at the output of the PRBS generator is applied to the first bit of the first Byte following the inverted MPEG-2 sync Byte (i.e.  $B8_{HEX}$ ). To aid other synchronisation functions, during the MPEG-2 sync Bytes of the subsequent 7 transport packets, the PRBS generation continues, but its output is disabled, leaving these Bytes unrandomised. The period of the PRBS sequence shall therefore be 1,503 Bytes.

The randomisation process is active also when the modulator input bit-stream is non-existent, or when it is non-compliant with the MPEG-2 transport stream format (i.e. 1 sync Byte + 187 packet Bytes). This is to avoid the emission of an unmodulated carrier from the modulator.

#### **Reed-Solomon coding**

Following the energy dispersal randomisation process, systematic shortened Reed-Solomon encoding is performed on each randomised MPEG-2 transport packet, with T = 8. This means that 8 erroneous Bytes per transport packet can be corrected. This process adds 16 parity Bytes to the MPEG-2 transport packet to give a codeword (204, 188).

NOTE: RS coding is applied also to the packet sync Byte, either non-inverted (i.e. 47<sub>HEX</sub>) or inverted (i.e. B8<sub>HEX</sub>).

Code Generator Polynomial:  $g(x) = (x+\lambda^0)(x+\lambda^1)(x+\lambda^2) \dots (x+\lambda^{15})$ , where  $\lambda = 02_{HEX}$

Field Generator Polynomial:  $p(x) = x^8 + x^4 + x^3 + x^2 + 1$

The shortened Reed-Solomon code is implemented by appending 51 Bytes, all set to zero, before the information Bytes at the input of a (255, 239) encoder; after the coding procedure these Bytes are discarded.

### **Convolutional interleaving**

Convolutional interleaving with depth I = 12 is applied to the error protected packets (see figure 2c). This results in an interleaved frame.

The convolutional interleaving process is based on the Forney approach which is compatible with the Ramsey type III approach, with I = 12. The Interleaved Frame is composed of overlapping error-protected packets and is delimited by MPEG-2 sync Bytes (preserving the periodicity of 204 Bytes).

The interleaver may be composed of I=12 branches, cyclically connected to the input Byte-stream by the input switch. Each branch is a First In First Out (FIFO) shift register, with depth (Mj) cells (where M=17=N/I, N=204= error protected frame length, I=12= interleaving depth, = branch index). The cells of the FIFO shall contain 1 Byte, and the input and output switches is synchronised.

For synchronisation purposes, the sync Bytes and the inverted sync Bytes are always routed into the branch 0" of the interleaver (corresponding to a null delay).

The de-interleaver is similar, in principle, to the interleaver, but the branch indexes are reversed (i.e. j=0 corresponds to the largest delay). The de-interleaver synchronisation can be carried out by routing the first recognised sync Byte into the "0" branch.

### **Electrical characteristics:**

### Electrical characteristics CCITT G.703 2048 Kb/s:

Pair each directionOne coaxial pair.Test load impedance75  $\Omega$  resistive.Signal level2.37 V.Nominal pulse width244 ns.Code conversionHDB3.Pulse shapeFig. 15/G.703.

Jitter at input port \$ 3 of recommendation G.823.

Jitter at output port \$ 2 of recommendation G.823.

Return loss at input ports:

51 KHz to 102 KHz 12 dB 102 KHz to 2048 KHz 18 dB 2048 KHz to 3072 KHz 14 dB

### Electrical characteristics CCITT G.703 8448 Kb/s:

Pair each directionOne coaxial pairTest load impedance $75 \Omega$  resistiveSignal level2.37 VNominal pulse width59 nsCode conversionHDB3Pulse shapeFig. 16/G.703

Jitter at input port § 3 of recommendation G.823 Jitter at output port § 2 of recommendation G.823

Return loss at input ports:

211 KHz to 422 KHz 12 dB 422 KHz to 8448 KHz 18 dB 8448 KHz to 12672 KHz 14 dB

### Electrical characteristics CCITT G.703 34368 Kb/s:

$\begin{array}{lll} \text{Cable type} & \text{Coaxial.} \\ \text{Impedance} & 75 \ \Omega \\ \text{Signal level} & 1.0 \ \text{V} \\ \text{Nominal pulse width} & 14.55 \ \text{ns} \\ \text{Code conversion} & \text{HDB3} \\ \text{Pulse shape} & \text{Fig. 17/G.703} \\ \end{array}$

Jitter at input port § 3 of recommendation G.823 Jitter at output port § 2 of recommendation G.823

Return loss at input ports:

860 KHz to 1720 KHz >12 dB 1720 KHz to 34368 KHz >18 dB 34368 KHz to 51550 KHz >14 dB

### Electrical characteristics CCITT G.703 Shaped 44736 Kb/s:

Cable type Coaxial. Impedance 75  $\Omega$

Signal level

Power at 22368 KHz +1.8 dBm to +5.7 dBm.

Power at 44736 KHz >20 dBm below power at 22368 KHz.

Code conversion B3ZS

Pulse shape Fig. 14/G.703

### Electrical characteristics CCITT G.703 Unshaped 44736 Kb/s:

$\begin{array}{ccc} \text{Cable type} & \text{Coaxial.} \\ \text{Impedance} & 75 \, \Omega \\ \text{Signal level} & 1.0 \, \text{V} \\ \text{Nominal pulse width} & 14.55 \, \text{ns} \\ \text{Code conversion} & \text{B3ZS} \\ \text{Pulse shape} & \text{Fig. 17/G.703} \\ \end{array}$

Jitter at input port § 3 of recommendation G.823 Jitter at output port § 2 of recommendation G.823

Return loss at input ports:

860 KHz to 1720 KHz >12 dB 1720 KHz to 34368 KHz >18 dB 34368 KHz to 51550 KHz >14 dB

### **Electrical characteristics SPI:**

### **Line Driver Characteristics (Source)**

$\begin{array}{ll} \text{Output impedance} & 100 \ \Omega \ \text{maximum} \\ \text{Common mode voltage} & 1.125 \ \text{V to } 1.375 \ \text{V} \\ \text{Signal amplitude} & 247 \ \text{mV to } 454 \ \text{mV} \\ \end{array}$

Rise and fall times  $\,$  < T/7, measured between the 20% and 80% amplitude points, with a 100  $\Omega$

resistive load. The difference between rise and fall times shall not exceed T/20.

### **Line Receiver Characteristics (Destination)**

$\begin{array}{ll} \text{Input impedance} & 90 \ \Omega \ \text{to} \ 132 \ \Omega \\ \text{Maximum input signal} & 2.0 \ \text{Vp-p} \\ \text{Minimum input signal} & 100 \ \text{mVp-p} \end{array}$

### **General Information on DVB-ASI**

For transport, the 270 Mb/s stream may be fed through DA's and switchers without regard for the underlying data rate, thus simplifying system design.

Note that the ASI signal is polarity sensitive. Although most 270 Mb/s SDI DA's and switchers will pass ASI signals, the line drivers used usually have both inverted and non-inverted outputs. For ASI, only those outputs that are non-inverted may be used.

### **Electrical characteristics ASI:**

### Transmitter output characteristics:

$\begin{array}{lll} \mbox{Output voltage} & 800 \ \mbox{mVp-p} \pm 10\%. \\ \mbox{Deterministic jitter} & <10\% \ \mbox{p-p}. \\ \mbox{Random jitter} & <8\% \ \mbox{p-p}. \\ \mbox{Rise/fall time } (20\text{-}80\%) & <1.2 \ \mbox{ns}. \\ \end{array}$

### **Receiver input characteristics:**

$\begin{array}{ll} \mbox{Minimum sensitivity (D21.5 idle pattern)} & 200 \ \mbox{mV} \\ \mbox{Maximum input voltage} & 880 \ \mbox{mVp-p} \\ \mbox{s}_{11} \mbox{ (range: 0.1 to 1.0 x bit rate)} & -17 \mbox{ dB} \end{array}$

Minimum discrete connector return loss 15 dB (5 MHz - 270 MHz)

Coaxial link:

Impedance 75 Ohm

Equipment connector BNC female

(Electrical measurements made with 75 Ohm resistive termination.)

### **References**

ANSI Standard X3T1 1/ Levels FC-1 and FC-0.

DVB-PI-232 TM1449 Interfaces for CATV/SMATV Headends & similar Professional Equipment.

ETS 300 421. Digital broadcasting systems for Television, sound and data services; framing structure, channel coding for 11/12 GHz satellite services.

ETS 300 429. Digital broadcasting systems for Television, sound and data services; framing structure, channel coding and modulation for cable systems.

ETS 300 473. Digital broadcasting systems for Television, sound and data services; Satellite Master Antenna Television (SMATV) distribution systems.

ISO/IEC 13818-1 (Systems). MPEG-2 Standard.

ITU-T Rec. G.703.

TM 1664 Rev 2 - DVB Interfaces for PDH Networks.

### Glossary of terms

8B/10B Eight to Ten Bit Conversion.

ASI Asynchronous Serial Interface.

ASI-C ASI Coaxial cable. ASI-O ASI Fibre optic cable.

B3ZS Bipolar with Three Zero Substitution.

BB Baseband. BER Bit Error Rate.

CCIR Comite Consultatif International des Radiocommunications.

CCITT Comite Consultatif International Telephonique et Telegraphique.

CPLD Custom Programmable Logic Device.

DJ Deterministic Jitter.

DTVC Digital Television by Cable.

DVB Digital Video Broadcasting.

DVG Digital Video Generator.

EBU European Broadcasting Union.

EBU European Broadcasting Union.

ETS European Telecommunication Standard.

ETSI European Telecommunications Standards Institute.

FEC Forward Error Correction.

FIFO First In First Out.

FPGA Field Programmable Gate Array.

G.703 ITU CCITT recommendation G.703.

HDB3 High Density Bi-polar of order 3.

IF Intermediate Frequency.

IRD Integrated Receiver Decoder.

ITU International Telecommunications Union.

LSB Least Significant Bit.

LVDS Low Voltage Differential Signalling.

Mb/s Megabits per second.

MPEG Moving Pictures Experts Group.

MPEG Motion Picture Experts Group.

MSB Most Significant Bit.

MSB Most Significant Bit.

MUX Multiplex.

NO Normally open contact set.

NC Normally closed contact set.

NRZ Non Return to Zero.

PDH Plesiochronic Digital Hierarchy.

PRBS Pseudo Random Binary Sequence.

QAM Quadrature Amplitude Modulation.

QEF Quasi Error Free.

QPSK Quarternary Phase Shift Keying.

R & S Rohde & Schwarz.

RF Radio Frequency.

RJ Random Jitter.

RS Reed Solomon.

SDI Serial Digital Interface.

SMATV Satellite Master Antenna Television. SPI Synchronous Parallel Interface MPEG2.

SSI Synchronous Serial Interface. TDM Time Division Multiplex.

TS Transport Stream.

TV Television.

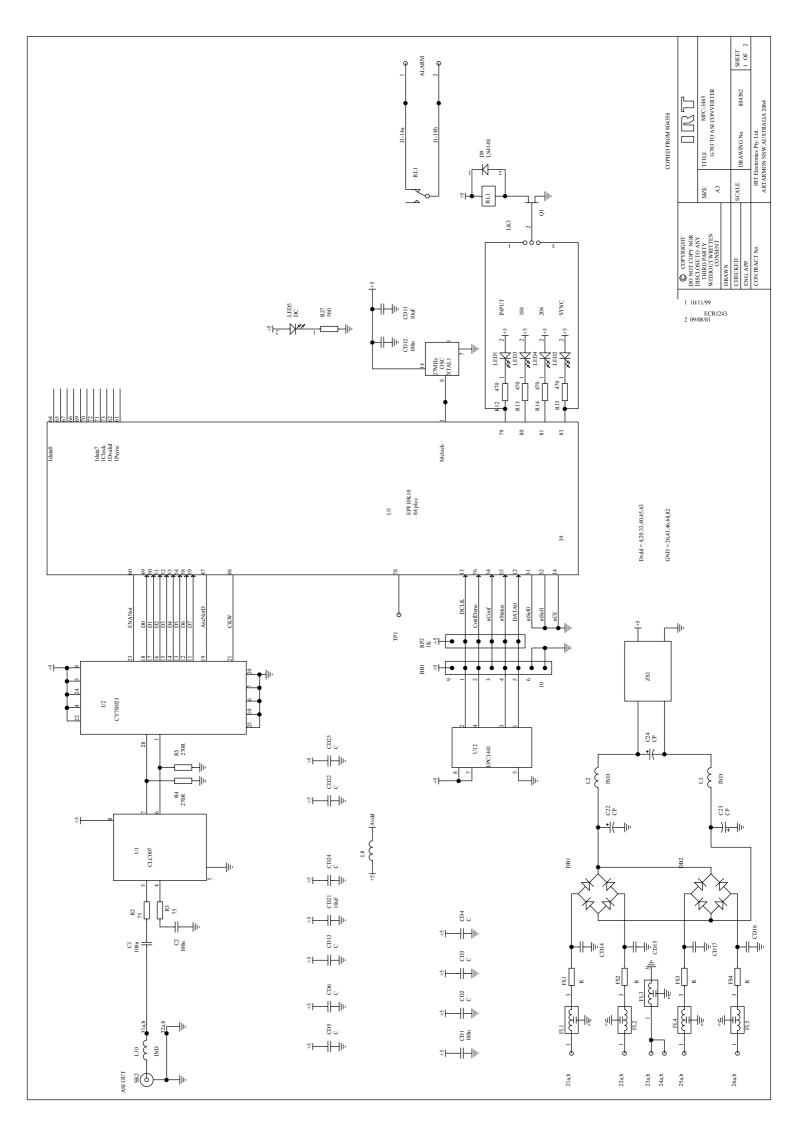

# **Drawing index**

| Drawing # | Sheet # | Description                                         |

|-----------|---------|-----------------------------------------------------|

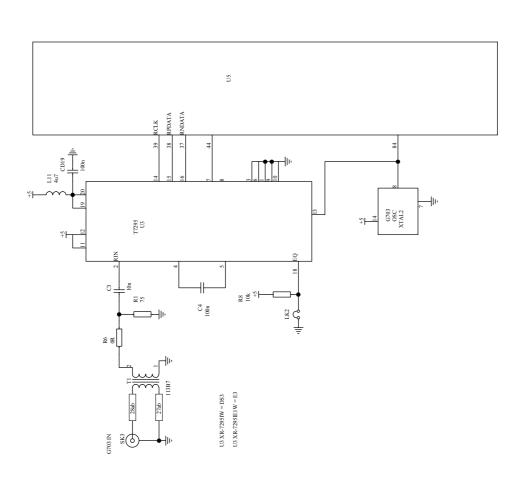

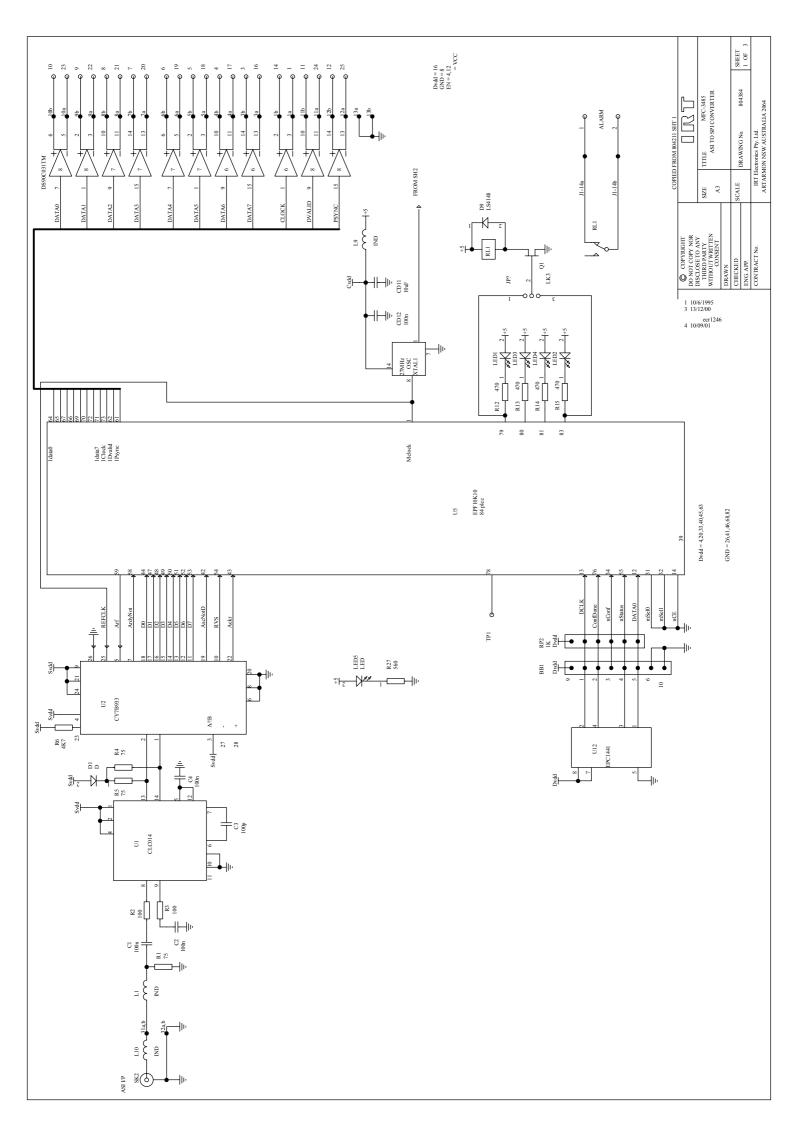

| 804382    | 1       | MFC-3465 circuit schematic – G.703 to ASI converter |

| 804382    | 2       | MFC-3465 circuit schematic – G.703 to ASI converter |

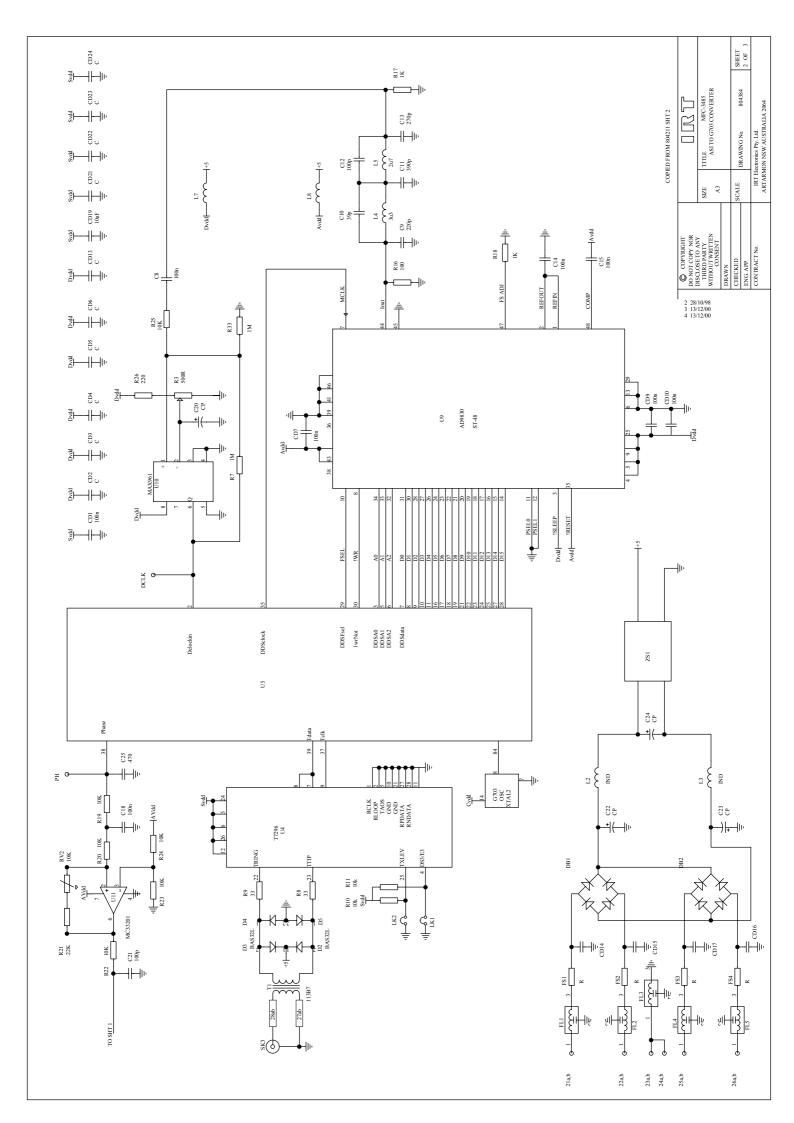

| 804384    | 1       | MFC-3485 circuit schematic – ASI to SPI converter   |

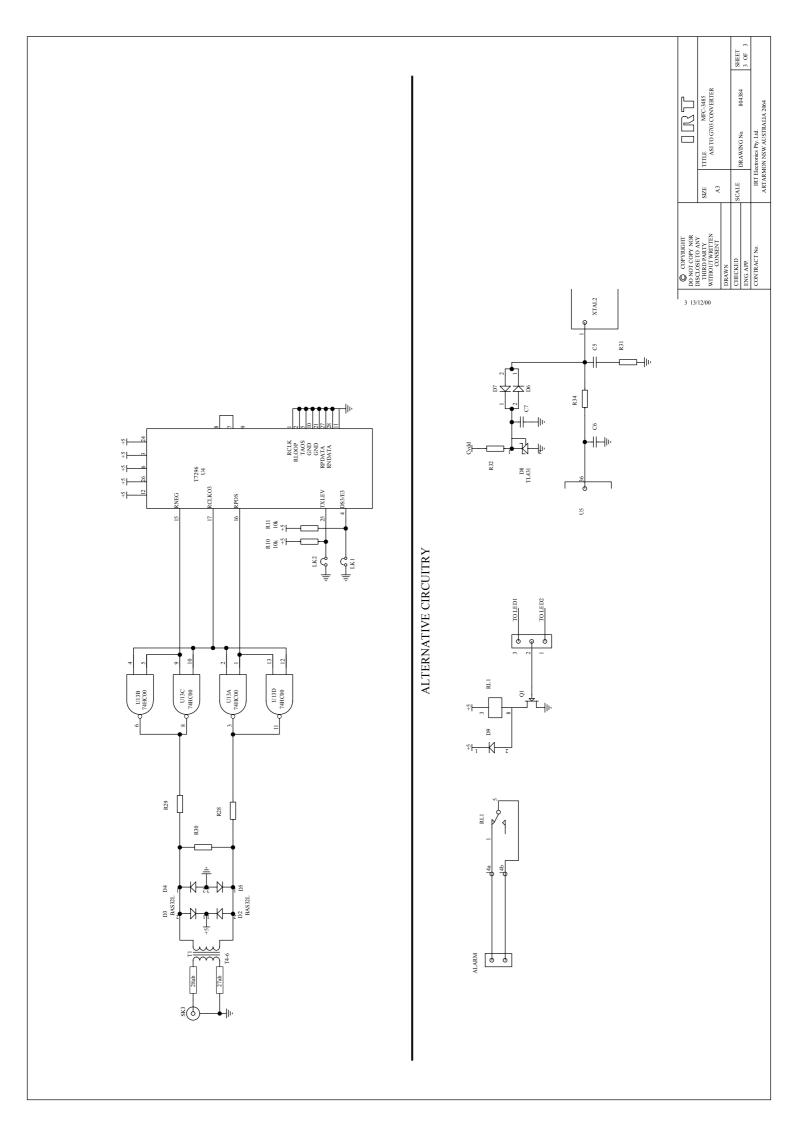

| 804384    | 2       | MFC-3485 circuit schematic – ASI to G.703 converter |

| 804384    | 3       | MFC-3485 circuit schematic – ASI to G.703 converter |

|                                                                                                              |                                         |  |                       | -      |                                                          |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|-----------------------|--------|----------------------------------------------------------|

|                                                                                                              |                                         |  | SHEET                 | 2 OF 2 |                                                          |

|                                                                                                              | TITLE MFC-3465<br>G703 TO ASI CONVERTER |  | COCAGO SIN CININA BAN | 792+00 | IRT Electronics Pty. Ltd.<br>ARTARMON NSW AUSTRALIA 2064 |

|                                                                                                              | SIZE<br>A3                              |  | SCALE                 |        | IRT EL<br>ARTARN                                         |

| © COPYRIGHT DD NOT COPY NOR DISCLOSE TO ANY THRO PARTY WITHOUT WRITTEN CONSENT CHECKED ENG APP. CONTRACT NO. |                                         |  |                       |        |                                                          |

| 2 28/10/98                                                                                                   |                                         |  |                       |        |                                                          |

| 3 13/08/01<br>ECR1243                                                                                        |                                         |  |                       |        |                                                          |